Texas Instruments TMS320F28P65x/TMS320F28P65x-Q1 Real-Time MCUs

Texas Instruments TMS320F28P65x/TMS320F28P65x-Q1 Real-Time Microcontrollers (MCUs) belong to the C2000™ real-time microcontroller family of scalable, ultra-low latency devices. The C2000 MCUs are developed for efficiency in power electronics, including but not limited to high power density and switching frequencies. Furthermore, the devices support using IGBT, GaN, and SiC technologies.

The TI TMS320F28P65x/TMS320F28P65x-Q1 microcontroller real-time control subsystem is based on the 32-bit C28x DSP core, which offers 200MIPS of signal processing performance in each core for floating- or fixed-point code running from either on-chip flash or SRAM. The TMS320F28P65x-Q1 devices are AEC-Q100 qualified for automotive applications.

Features

- Real-time Processing

- Contains up to three CPUs: two 32-bit C28x DSP CPUs and one CLA CPU, all running at 200MHz

- Delivers a total processing power equivalent to 1000MHz Arm® Cortex®-M7 based device on real-time signal chain performance

- C28x DSP architecture

- IEEE 754 double-precision (64-bit) FloatingPoint Unit (FPU)

- Trigonometric Math Unit (TMU)

- Fast Integer Division (FINTDIV)

- CRC engine and instructions (VCRC)

- Control Law Accelerator (CLA) CPU

- IEEE 754 single-precision floating-point

- Executes code independently of C28x CPUs

- Analog Subsystem

- Three Analog-to-Digital Converters (ADCs)

- 16-bit mode, 1.19MSPS each

- 12-bit mode, 3.92MSPS each

- Up to 40 single-ended or 19 differential inputs

- Separate sample-and-hold (S/H) on each ADC to enable simultaneous measurements

- Hardware post-processing of conversions

- Hardware oversampling (up to 128x) and undersampling modes, with accumulation, averaging and outlier rejection

- 24 redundant input channels for flexibility

- Automatic comparison of conversion results for functional safety applications

- 11 windowed comparators with 12-bit Digital-to-Analog Converter (DAC) references

- DAC with slope compensation - enabling peak current and valley current mode control

- Connection options for internal temperature sensor and ADC reference

- Two 12-bit buffered DAC outputs

- Two CAN FD/MCAN Controller Area Networks with flexible data rate

- Three Analog-to-Digital Converters (ADCs)

- System Peripherals

- Two 6-channel Direct Memory Access (DMA) controllers

- 185 individually programmable multiplexed General-Purpose Input/Output (GPIO) pins

- Expanded Peripheral Interrupt controller (ePIE)

- Low-power mode (LPM) support

- Embedded Real-time Analysis and Diagnostic (ERAD)

- Background CRC (BGCRC)

- Security Peripherals

- Advanced Encryption Standard (AES-128, 192, 256) accelerator

- Security

- JTAGLOCK

- Zero-pin boot

- Dual-zone security

- Unique Identification (UID) number

- Safety Peripherals

- Easier implementation with Reciprocal comparison

- Lockstep on C28x CPU 2

- Memory Power-On Self-Test (MPOST)

- Hardware Built-in Self-Test (HWBIST)

- Functional Safety-Compliant targeted

- Developed for functional safety applications

- Documentation will be available to aid ISO 26262 and IEC 61508 system design

- Systematic capability up to ASIL D and SIL 3 targeted

- Hardware capability up to ASIL B and SIL 2 targeted

- Safety-related certification

- ISO 26262 and IEC 61508 certification up to ASIL B and SIL 2 by TÜV SÜD planned

- Clock and System Control

- Two internal 10MHz oscillators

- On-chip crystal oscillator

- 2*APLL, BOR, Redundant interrupt vector RAM

- Windowed watchdog timer module

- Missing clock detection circuitry

- Dual-clock Comparator (DCC)

- Live Firmware Update (LFU)

- Fast context switching from old to new firmware with or without a power cycle

- 1.2V core, 3.3V I/O design

- Internal VREG for 1.2V generation

- Brownout reset (BOR) circuit

- Memory

- 1.28MB of CPU-mappable flash (ECC-protected) with five flash banks

- 248KB of RAM (Enhanced Parity-protected)

- External Memory Interface (EMIF) with ASRAM, SDRAM support, or ASIC/FPGA

- Control Peripherals

- 36 Pulse Width Modulator (PWM) channels, all with 150ps high-resolution capability (HRPWM)

- Minimum Dead-Band Logic (MINDB), Illegal Combo Logic (ICL), and other special features (that is, Diode Emulation [DE]) support

- Enable Matrix Converters, Multilevel Converters, and Resonant Converters support without additional external logic

- Seven Enhanced Capture (eCAP) modules

- High-resolution Capture (HRCAP) is available on two of the seven eCAP modules

- Two new monitor units for edge, pulse width, and period that can be coupled with ePWM strobes and trip events

- Increased 256 inputs for more capture options

- New ADC SOC generation capability

- eCAP can also be used for additional PWM

- Six Enhanced Quadrature Encoder Pulse (eQEP) modules

- 16 Sigma-Delta Filter Module (SDFM) input channels, two independent filters per channel

- Embedded Pattern Generator (EPG)

- Configurable Logic Block

- Six logic tiles to augment existing peripheral capability or define customized logic to reduce or remove external CPLD/FPGA

- Supports Encoder interfaces without the need for FPGA

- Enables customized PWM generation for power conversion

- 36 Pulse Width Modulator (PWM) channels, all with 150ps high-resolution capability (HRPWM)

- Communications Peripherals

- EtherCAT® SubordinateDevice (or SubDevice) Controller (ESC)

- USB 2.0 (MAC + PHY)

- Fast Serial Interface (FSI) enabling up to 200Mbps data exchange across isolation

- Four high-speed (up to 50MHz) SPI ports

- Four Serial Communications Interfaces (SCI) (support UART)

- Two high-speed (25Mbps) Universal Asynchronous Receiver/Transmitters (UARTs)

- Two I2C interfaces (400Kbps)

- External boot option via SPI/ SCI/I2C

- Two UART-compatible Local Interconnect Network (LIN) Modules (support SCI)

- Power-Management Bus (PMBus) interface (supports I2C)

- One Controller Area Network (CAN/DCAN)

- Package options:

- Lead-free, green packaging

- 256-ball New Fine Pitch Ball Grid Array (nFBGA) [ZEJ suffix], 13mm × 13mm/0.8mm pitch

- 176-pin PowerPAD™ Thermally Enhanced Low profile Quad Flatpack (HLQFP) [PTP suffix], 26mm × 26mm/0.5mm pitch

- 169-ball New Fine Pitch Ball Grid Array (nFBGA) [NMR suffix], 9mm × 9mm/0.65mm pitch

- 100-pin PowerPAD™ Thermally Enhanced Thin

- Quad Flatpack (HTQFP) [PZP suffix], 16mm × 16mm/0.5mm pitch

- Temperature Ambient (TA) of -40°C to 125°C (industrial and automotive qualified)

Applications

- Servo drive control module

- Robot Servo Drive

- CNC control

- Mobile robot motor control

- HVAC large commercial motor control

- Linear motor segment controller

- Central inverter

- String inverter

- Power Conversion System

- DC Fast Charging Station

- Inverter and motor control

- Industrial AC-DC

- Three phase UPS

- Single-phase online UPS

- Merchant network and server PSU

- On-board (OBC) and wireless charger

- Automotive HVAC compressor module

- Headlight

Videos

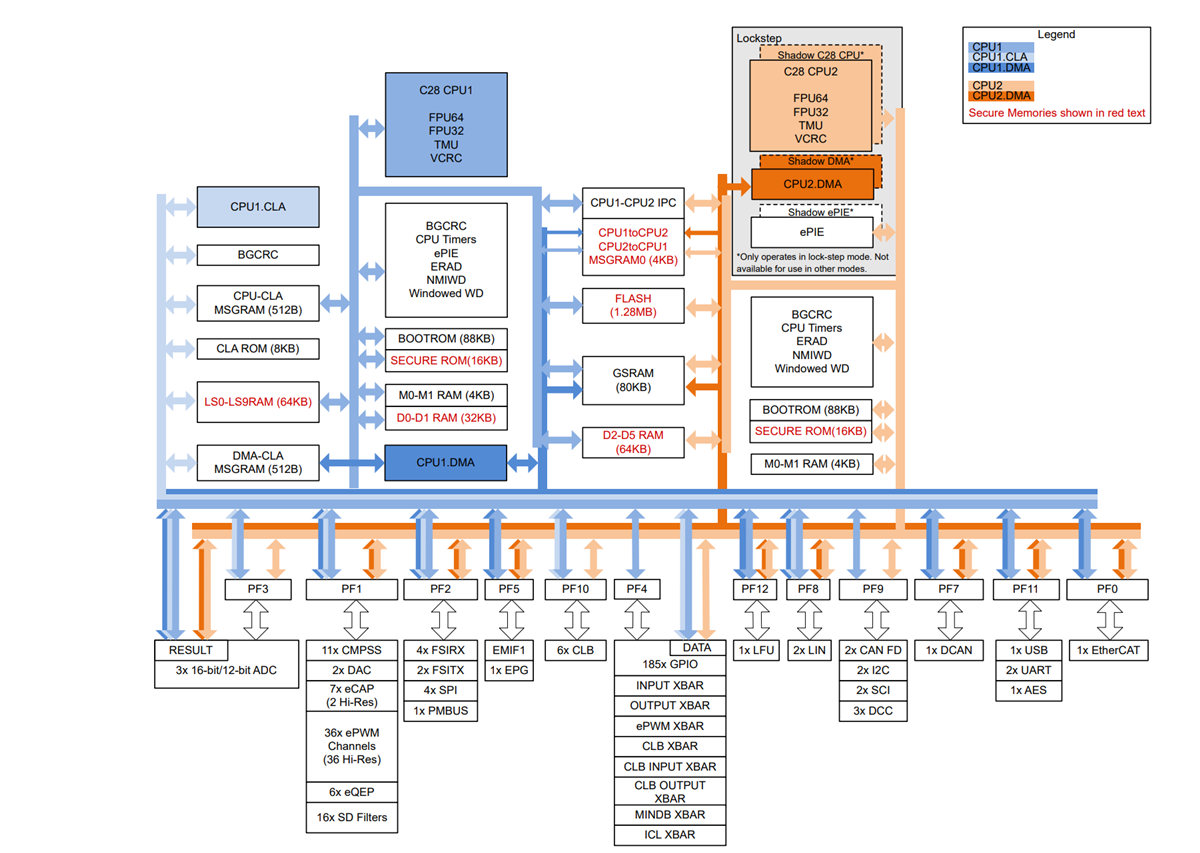

Functional Block Diagram